Abstract: This paper introduces an FPGA-based Down Scaler video system design. The core components of the system use the Xilinx Kintex-7 onboard XC7K325T chip, and the system design uses Vivado tools, including the Downscaler module design using Vivado HLS. First, the C/C++ code of the Down Scaler module is written according to the code specification of Vivado HLS. Then, the RTL level code and the integrated result Down Scaler IP core are generated by the compiler tool, and the Down Scaler IP core and the Xilinx video IP such as TPG and VDMA are finally used. Nuclear interconnects to build real-time video systems. Under the condition of meeting real-time requirements and FPGA resource consumption requirements, the design realizes the transplantation of Down Scaler video algorithm from PC-side software processing to FPGA platform hardware processing. INTRODUCTION In the field of electronic design automation, high-level synthesis tools are becoming more and more popular, which can translate functions of high-level languages ​​such as C/C++, SystemC, and Matlab into RTL-level code. The abstraction layer of the design is further enhanced. As the complexity of embedded systems increases, high-level synthesis tools begin to penetrate the design process of electronic systems, especially embedded systems. This paper introduces a Down Scaler video system design based on Xilinx's high-level synthesis tool Vivado HLS. 1 High-level comprehensive overview In the past 20 years, in the dominant electronic design process, hardware designers need to manually complete everything from system function indicators to RTL-level code. Nowadays, such a design process begins to become difficult, because more and more functions can be integrated on one chip. According to the traditional design process, it becomes more and more difficult for developers to complete all the functions by themselves, but because of the design function Increasing the number of people in the design team is not economically viable, which means that design productivity must be improved. High-level synthesis can improve design productivity by automating from the algorithm layer to the RTL layer. As can be seen from Figure 1(b), the application of high-level synthesis reduces the distance from the functional indicators to the beginning of the automated design process. In the design process, the application of high-level synthesis tools can bring the following conveniences to the design work: First, the amount of code written by the designer is significantly reduced, and the error rate is reduced while shortening the development cycle. Secondly, in today's product development process, the time required for verification often exceeds the design time. Using high-level synthesis tools can shorten the verification time. When the high-level synthesis tool generates the design code, it can also generate the test platform code. You can verify that the design code is correct by testing the data directly. 2Down Scaler module design The traditional Down Scaler operation is performed under the PC architecture. Take the THVN VS7000 product of Thomson Video Network, for example, the Down Scaler module is a C++ application in the PC server, before the operation processing. The acquisition of the video stream is implemented by a Black Magic board, and the pixel information of each received image is transmitted to the PC server through PCIe. The server first stores the pixel information in three unused memory spaces Y, U, and V, and then the application Down Scaler performs arithmetic processing on the pixel information of the three spaces. The design goal described in this paper is to implement a "hardware processing" of the video stream using a Down Scaler IP core in the FPGA, instead of the "software processing" of the image by the Downscale C++ program on the traditional PC side, thereby canceling the complete frame pixel information Y. Pre-storage steps for U, V components. 2.1 Module parameters require the video reduction ratio is 2/3, the pixel phase number is 2, according to the phase number, luminance chrominance, horizontal vertical, there are a total of 8 filter windows, each filter window contains 11 The parameters are determined in advance by the Lanczos algorithm, and the "mirror" processing is performed for 5 pixels of the edge of the image. 2.2 Module design key points

We can provide the CBD Vape Device/Battery, you can match them with our other CBD cartridges.

CBD does not have the psychoactive effect of THC, and its medical value is very high. Many studies have confirmed that CBD is used for

different symptoms and has pharmacological effects such as anti-spasm, anti-anxiety, anti-inflammatory, and pain relief.

cbd vape pen device, cbd vape battery pen, vape devices for cbd, cbd vape pod battery,cbd vape device disposable Ningbo Autrends International Trade Co.,Ltd. , https://www.supervapebar.com![Figure 1 High-level synthesis of Gasjki-Kuhn Y-chart diagram description [1]](http://i.bosscdn.com/blog/16/43/42/H25_0.jpg)

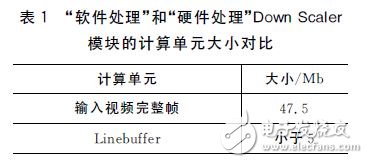

2.2.1 Calculation Unit According to the parameter requirements, the Down Scaler module includes two BRAM calculation units, namely Window and Linebuffer. Window is a one-dimensional storage space for storing 11 pixels. Linebuffer is a two-dimensional storage space for storing 11 rows of pixels. The Linebuffer receives new input pixels at each operating frequency. The previous pixels move to a position below the storage space at each operating frequency, that is, the newly received pixels are always stored in the initial position in the Linebuffer. When the Linebuffer fills up, the Downscaling operation begins, that is, 11 sample pixels are stored through the Window, and the pixel information is filtered. Compared with the "software processing" method of storing a complete image after a frame, the use of Linebuffer and Window as a "hardware processing" storage unit greatly reduces the module's storage space requirements. The calculation unit size pairs for the "Software Processing" and "Hardware Processing" Down Scaler modules are listed in Table 1.