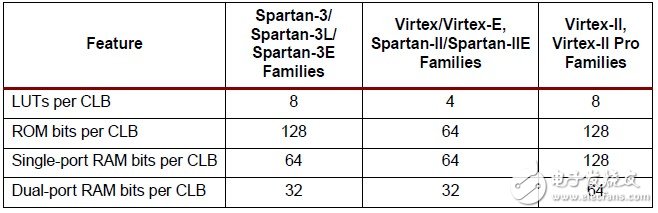

The basic characteristics of distributed RAM in Spartan-3 series FPGAs are briefly introduced. Why not start with the more advanced Virtex series? I took a closer look at the introduction and comparison of each series. The Spartan series is basically a streamlined version of the Virtex series. The basic principle is the same, so it is a good idea to start from a simple one. As for the specific configuration of each device, look up their respective Datasheet or User guide on the Xilinx website (this is also the learning resource I recently highlighted in the resource). Table 1 shows the basic comparison of distributed RAM in Spartan and Virtex series. 2D Handheld Barcode Scanner,2D Handheld Scanner,Munbyn Android Barcode Scanner,Zebra Ds2208 Scanner Guangzhou Winson Information Technology Co., Ltd. , https://www.barcodescanner-2d.com

Building Distributed RAM Using LUT in 3 Series FPGAs (3)

Table 1 Basic comparison of distributed RAM in Spartan and Virtex series

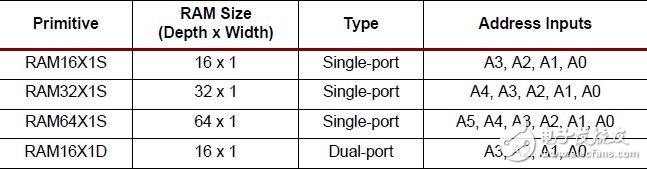

There are four primitives for SRAM and DRAM in the Spartan3 series FPGAs in the Xilinx library, as shown in Table 2. (Uncles who can call the primitives can refer to and). A detailed description of these primitives is available in the Spartan-3 Libraries Guide for HDL Designs, UG607.pdf. Table 2 Primitives of distributed RAM in the library

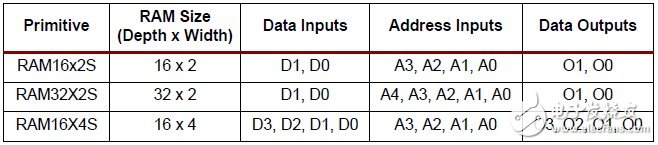

When the primitives in Table 2 are called, their inputs and outputs are 1 bit wide. In order to implement larger memory functions, they can be used in parallel, as shown in Table 3. When calling CoreGenerator, the definition of each port will be described in detail. It will not be described in detail here. Please refer to the help of CoreGenerator when the primitive is called or UG607.pdf above. Table 3 Parallel use of distributed RAM primitives

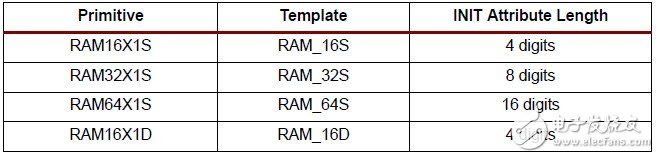

The distributed RAM is all zeros after device initialization. If you require a non-zero condition after initialization, you need to use the INIT attribute. Each INIT is a vector encoded in hexadecimal, sorted from MSB to LSB. Table 4 gives the INIT length for each primitive. Table 4 INIT length of each primitive

Each Spartan-3 FPGA's CLB contains 4 slices, which can be seen in the location datasheet, user guide, or PlanAhead. In comparison, PlanAhead is more intuitive, you can refer to Figure 5 in the figure. Distributed RAM is only located in SLICEM type SLICE, where "M" means that this slice supports memory-related functions; and L in SLICEL indicates that this type of slice only supports logic.