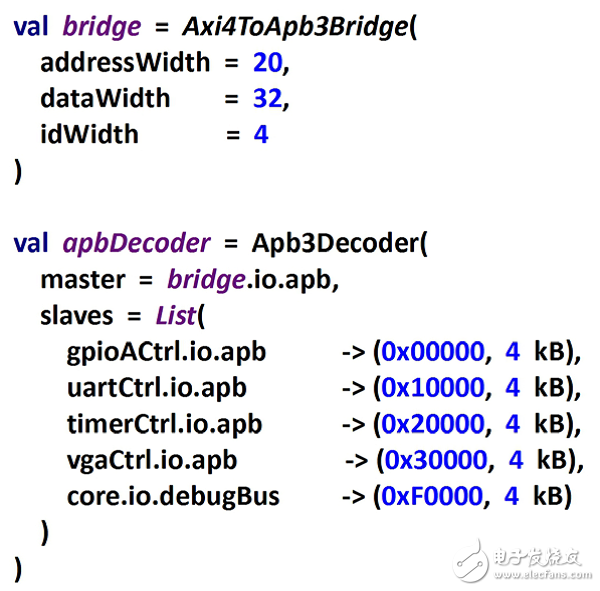

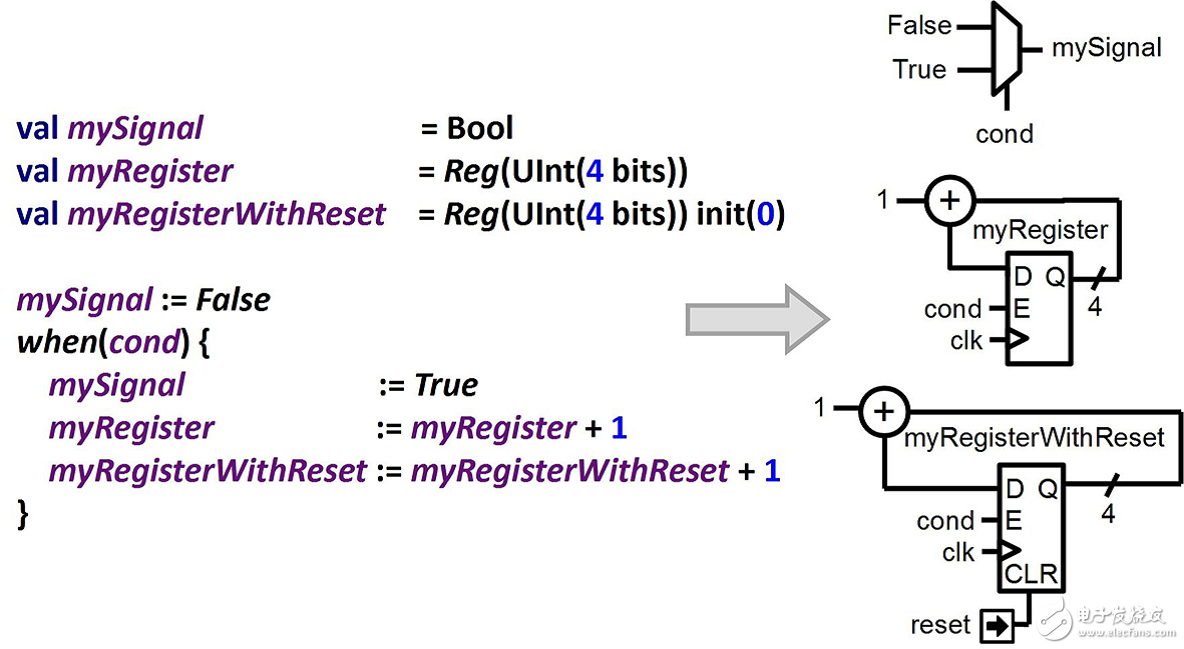

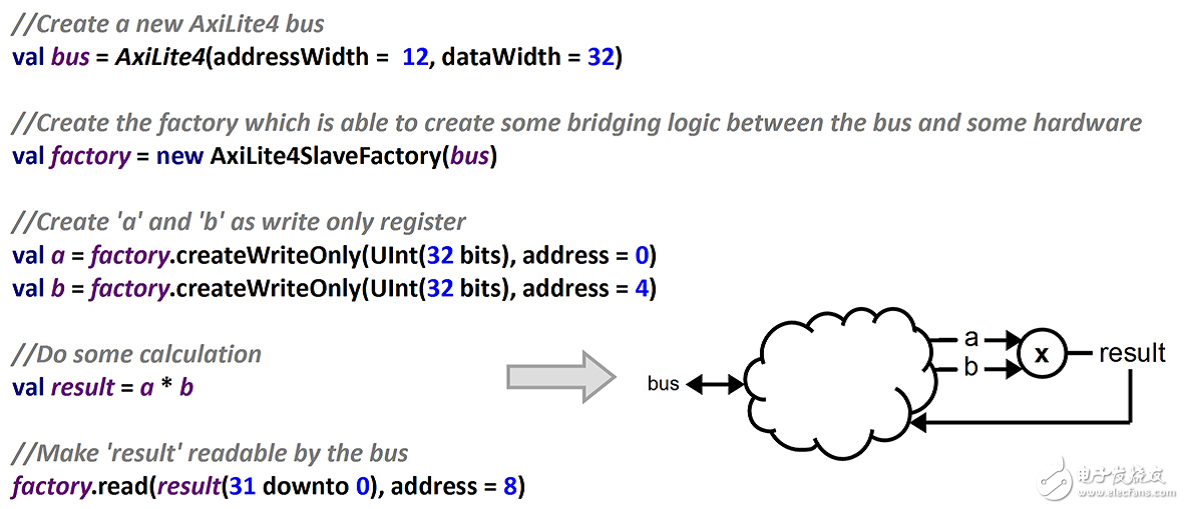

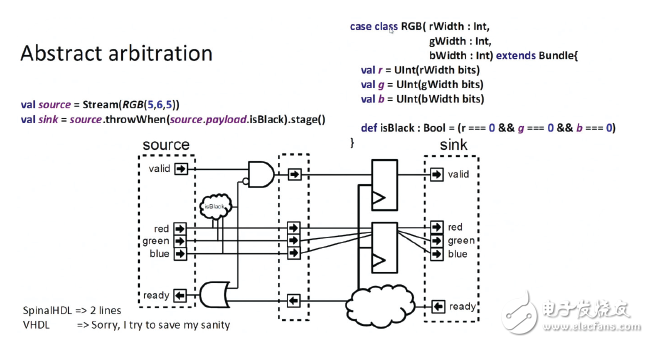

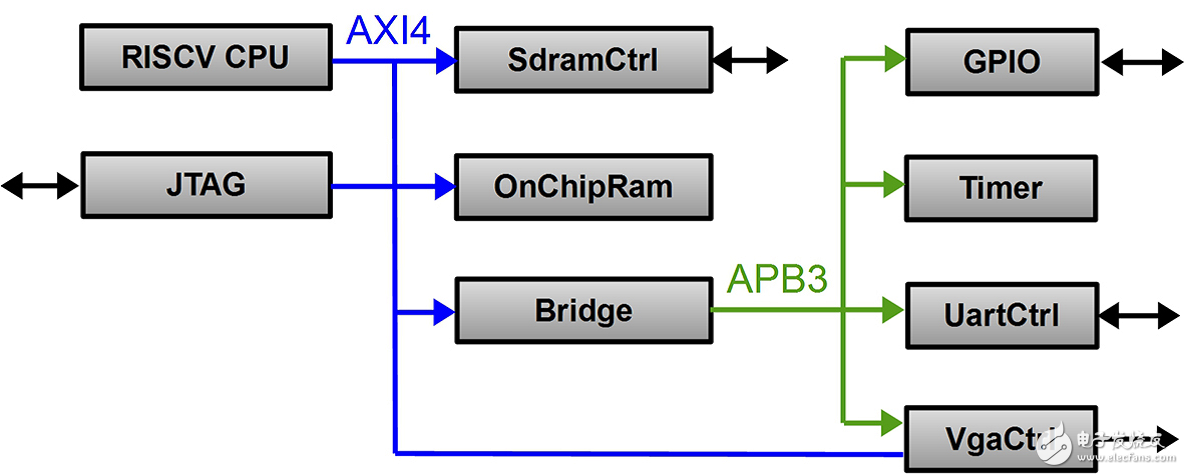

VHDL and Verilog are the two main languages ​​used to describe synthesizable digital hardware. But we should not forget that they were not originally created for this purpose, but for simulation and archiving. This fact, combined with many other grammatical weaknesses, raises many questions, such as weak design parameterization; poor design reusability; lengthy code, cumbersome methods; and ambiguous boundaries between synthesizable and non-integratable features. In response to these limitations and problems, new alternative solutions have emerged, such as Bluespec, Chisel, CλaSH, Migen, MyHDL, and SpinalHDL. Like VHDL and Verilog, SpinalHDL can be used to describe hardware by defining registers and gates. Instead of using well-known event-driven paradigms to describe hardware (such as VHDL and Verilog), SpinalHDL uses a syntax designed for this purpose. This allows the combination of signals and registers to be distinguished in their declarations and to define hardware behavior by defining rules. This means that signals and registers can be allocated in the same conditional statement, which is not possible with "event-driven" alternatives (see Figure 1). All the syntax of a language can be used for hardware description, and the syntax can be divided into two categories. One is: explicit synthesis hardware is defined by using a special type; the other is: it can be used to illustrate hardware structures such as instance loops, functions, and classes. In addition, the SpinalHDL compiler will perform a number of checks to ensure that the user design is legal, for example: whether there is a lack of a combination loop; the integrity of all combination assignments, to avoid unnecessary indenting latches; Legitimacy of connections across clock domains, etc. - This makes SpinalHDL safe to use. But the main difference between SpinalHDL and VHDL and Verilog is the fact that it is embedded in the general language (Scala). Because of this approach, we get a "Meta HDL" in which high-level parts (classes, dynamic arrays, dictionaries...) can be used to generate synthesizable hardware descriptions by means of algorithms. This provides a very high level of expressiveness to describe flexible and reusable hardware. In fact, it is it that enables SpinalHDL to manipulate every element of the described design in an object-oriented and functional programming manner; it is combined with a capable standard library to obtain the meta-hardware description and presentation capabilities. Unexpected ability, far beyond VHDL, Verilog and SystemVerilog (see Figure 2). The SpinalHDL compiler converts user-written hardware descriptions into human-readable and synthesizable VHDL/Verilog netlists (as most schematic input tools use), making it compatible with most EDA tools used in the industry. . In addition, the target language/EDA tool does not need to natively support all of the advanced features provided by Spinal-HDL (such as type and data structure parameterization), which are internal to the SpinalHDL compiler before being decompressed/expanded to the generated VHDL/Verilog netlist. Supported and resolved (see Figure 3). As a realistic presenter of these concepts, we implemented a small SoC called "Pinsec" using SpinalHDL, which integrates RISC-V CPU, SDRAM controller, embedded RAM, GPIO, timer, UART, VGA and JTAG. The debug interface is interconnected by AXI4 and APB3 interconnects (see Figure 4). This demonstration shows that the top level of the design can be implemented very easily, especially when it comes to parameterization and instantiation of bus interconnects. Unlike traditional methods, SpinalHDL can be done with just a few lines of code, which greatly improves readability and productivity. For example, connecting a new peripheral to an APB interconnect requires only one row of parameterization code (see Figure 5). Figure 5: Pinsec's bus bridge and top-level instantiation of all APB3 bus constructs. Another interesting demonstration is the second iteration of the RISC-V CPU (named VexRiscv), demonstrating the gain from using the advanced meta-hardware description capabilities of SpinalHDL. First, the CPU top layer is a blank skeleton that provides only a number of elaboration services, an automatic pipeline as a signal through stages, and an arbitration interface for each stage. Combined with a plug-in registration system that allows hardware to be injected at the top level of the CPU, this approach supports a very flexible CPU architecture that can have multiple variants of the same functionality without the need to integrate it into the CPU code. Plugins can range from the simplest things (such as program counters or integer ALUs) to the most complex operations (such as loading and storage support via L1 cache). The cooperation between plugins can also be very complicated. For example, all plugins can issue new instruction opcodes and how they are decoded by the instruction decoder. The instruction decoder will then use the Quine-Mc Cluskey algorithm combined with the SpinalHDL meta-hardware functionality to generate the minimum instruction decode logic. Using SpinalHDL is an experience that changes the vision of digital hardware design and enables true engineering. With all its features, it allows chip designers to describe elegant and reusable hardware without the tedium and limitations of the commonly used HDLs such as VHDL, Verilog or even System-Verilog. It also demonstrates the feasibility and benefits of using a software engineering technique to describe the hardware structure without any overhead in the generated RTL. The language and its reference compiler are also completely free and open source. Finally, please note that all of the utilities and classes used in the above examples, such as Stream, RGB, Queue, Apb3Decoder, AxiLite4, and AxiLite4SlaveFactory, are not provided in the Spinal-HDL language, but are provided by the standard library using its regular syntax. In other words, you can extend the language itself by implementing new libraries, abstraction layers, and tools that can fundamentally improve the expressive power of hardware descriptions; you can also extend the language by introducing new concepts without ignoring abstract hardware ( Because these libraries are still implemented in the RTL domain). Water Purifier,Intelligent Temperature Control Water Purifier,Water Filter Purifier,Home Use Water Purifier Shandong Sangle Group Co.,Ltd. , https://www.sangle-group.com

Figure 1: A simple hardware description.

Figure 2: Using an abstract implementation register bank.

Figure 3: Implementation of the arbitration pipeline.

Figure 4: Pinsec SoC block diagram.